Creating Versatile and Efficient HD/4K/8K Video Solutions

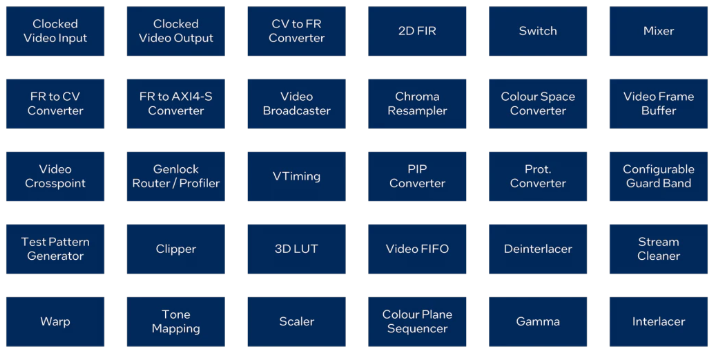

The Video and Vision Processing Suite features IPs that range from simple building block functions such as clocked video and genlock suite, color space conversion, and mixer to sophisticated processing functions that can implement programmable scaling, arbitrary non-linear distortion correction, 3D look-up table, adaptive tone mapping and many more.

- All the Video and Vision Processing IPs use Intel® FPGA streaming video data interfaces for video I/O, based on the industry standard AXI4-Stream protocol.

- You can mix and match video and image processing IPs with your own proprietary IP.

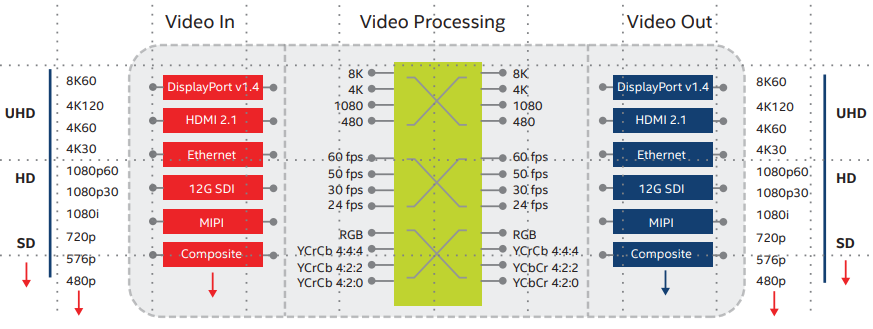

- Utilizing Intel® Agilex™ FPGA architecture – the Video and Vision Processing Suite is capable of processing 8K video at 60fps with four pixels in parallel at 600MHz.

- Support for processing flexibility of 1-8 pixels in parallel.

- Support for 1-4 color symbols per pixel and RGB and YCbCr 444, 422 and 420 color spaces.

- Data precision of 8-16 bits per symbol.

- Video fields with 1-16384 pixels in both height and width.

Avalon memory-mapped agent interfaces for runtime control and Avalon memory-mapped host interface for external memory usage allow push-button conversion in Intel Platform Designer to industry standard AXI4-S or AXI4-Stream memory mapped interfaces if required.

- You can use Video and Vision Processing IP to build a custom video and image processing signal chain using the Platform Designer, as well as to automatically integrate embedded processors and peripherals and generate arbitration logic.

IP Cores in the Video & Vision Processing (VVP) IP Suite

See the full complement of cores below such as the new Tone Mapper and Warp IP cores which offer new creative ways to produce high-quality video. And the Intel Agilex FPGA family enables video solutions for resolutions up to 8K/60.

FPGA resource requirements, performance, and core details for each are in the Intel VVP Suite User Guide.

Get the Intel VVP Suite User Guide

Read the Intel FPGA Streaming Video Protocol Specification

Versatility of Rates and Interfaces

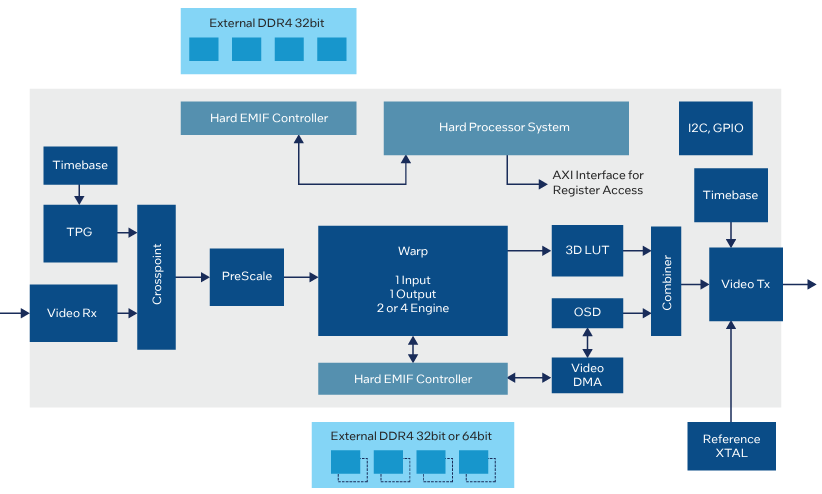

Intel SoC FPGA-based Example: Camera or video source input, output to monitor or projector.

Example Designs

Example designs are included in User Guides for the interface IP (HDMI, Display Port, SDI, MIPI…).

Contact Macnica for further information.

Learn More

Whitepaper: Agilex FPGAs Enable Efficient 4K/8K Video

Solution Brief: Intel FPGAs & Video Innovation

Whitepaper: FPGAs for Live Video Production

Ordering Information

Contact Macnica Sales for ordering information